クロック周り3

2007年7月23日

ip++信号を、Prep4Read 信号近くに作成した。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

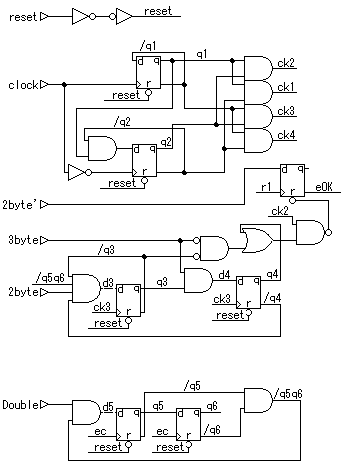

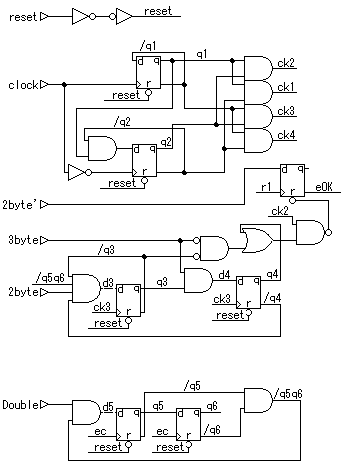

一番下の回路がそれで、FFを一つ追加して、実行を遅らせることにした。また、ck3をベースにしたexec 信号の生成が3番目・4番目のFF(同様にck3をクロックとして用いている)からのシグナルを基に作成されているのが気持ち悪かったので、少し早めのck2を利用しているRead1st信号を利用したFFを一つ追加してそのシグナル(eOK)を使うことにした。なお、2byte' 信号は1バイト目のレジスタの保存データではなく、1バイト目を読み出すときのデータライン由来。

exec周りは、次のとおり。

シミュレーションの結果は、このとおり。前回の回路と違い、Prep4Exec2 が上がるときには、Prep4Exec は上がらないようになったので、注意。

(追記)ダブルクロックの際、push/pop 命令で sp--/sp++ が一回余分に出るので、直さないといけない。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

一番下の回路がそれで、FFを一つ追加して、実行を遅らせることにした。また、ck3をベースにしたexec 信号の生成が3番目・4番目のFF(同様にck3をクロックとして用いている)からのシグナルを基に作成されているのが気持ち悪かったので、少し早めのck2を利用しているRead1st信号を利用したFFを一つ追加してそのシグナル(eOK)を使うことにした。なお、2byte' 信号は1バイト目のレジスタの保存データではなく、1バイト目を読み出すときのデータライン由来。

exec周りは、次のとおり。

シミュレーションの結果は、このとおり。前回の回路と違い、Prep4Exec2 が上がるときには、Prep4Exec は上がらないようになったので、注意。

(追記)ダブルクロックの際、push/pop 命令で sp--/sp++ が一回余分に出るので、直さないといけない。